Instrucciones de tiempo en AVR de 8-bit

La unidad de procesamiento central (CPU) del AVR es impulsada por el clkCPU del reloj de la CPU, generado directamente a partir de la fuente de reloj seleccionada para el chip. No se usa división de reloj interno. La arquitectura de Harvard y el concepto de archivo de registro de acceso rápido habilitan recuperaciones de instrucción en paralelo y ejecuciones de instrucción. Este es el concepto de canalización básico para obtener hasta 1 MIPS por MHz con los resultados únicos correspondientes para funciones por costo, funciones por reloj y funciones por unidad de potencia.

Las capturas de instrucción paralela y las ejecuciones de instrucción

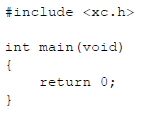

Comentarios

Publicar un comentario