El núcleo de los Microcontroladores AVR de 8 bits

La función principal del núcleo de la Unidad central de proceso (CPU) de AVR es garantizar la ejecución correcta del programa. Por lo tanto, la CPU debe poder acceder a las memorias, realizar cálculos, controlar periféricos y manejar interrupciones.

Diagrama de bloques de la arquitectura AVR

Núcleo AVR

Para maximizar el rendimiento y el paralelismo, el AVR utiliza una arquitectura Harvard, con memorias y buses separados para programas y datos. Las instrucciones en la memoria del programa se ejecutan con un solo canal de canalización. Mientras se está ejecutando una instrucción, la siguiente instrucción se realiza previamente desde la memoria del programa. Este concepto permite que las instrucciones se ejecuten en cada ciclo de reloj. La memoria del programa es la memoria flash reprogramable dentro del sistema.

Registros

El archivo de registro de acceso rápido contiene registros de trabajo de propósito general de 32 x 8 bits con un solo tiempo de acceso al ciclo de reloj. Seis de los 32 registros se pueden utilizar como tres punteros de registro de direcciones indirectas de 16 bits para el direccionamiento del espacio de datos, lo que permite cálculos de dirección eficientes. Uno de estos punteros de dirección también se puede usar como un puntero de dirección para buscar tablas en la memoria del programa Flash. Estos registros de funciones adicionales son los registros X, Y y Z de 16 bits.

Unidad de lógica aritmética (ALU)

La unidad de lógica aritmética (ALU) admite operaciones aritméticas y lógicas entre registros o entre una constante y un registro. El tiempo de acceso del ciclo de reloj individual permite el funcionamiento de ALU de ciclo único. En una operación típica de ALU, se emiten dos operandos desde el archivo de registro, la operación se ejecuta y el resultado se almacena nuevamente en el archivo de registro, en un ciclo de reloj. Las operaciones de registro único también se pueden ejecutar en la ALU. Después de una operación aritmética, el Registro de estado se actualiza para reflejar información sobre el resultado de la operación. El flujo del programa es proporcionado por instrucciones de saltos y llamadas condicionales e incondicionales, capaces de direccionar directamente todo el espacio de direcciones. La mayoría de las instrucciones de AVR tienen un solo formato de palabra de 16 bits. Cada dirección de memoria del programa contiene una instrucción de 16 o 32 bits.

Memoria

Los espacios de memoria en la arquitectura AVR son todos los mapas de memoria lineal y regular.

El espacio de la memoria del programa está dividido en dos secciones, la sección del programa de arranque y la sección del programa de la aplicación. Ambas secciones tienen bits de bloqueo dedicados para escritura y protección de lectura / escritura. La instrucción SPM que escribe en la sección de memoria Flash de la aplicación debe residir en la sección Programa de inicio.

Durante las interrupciones y las llamadas a la subrutina, el Contador de programa (PC) de la dirección de retorno se almacena en la Pila. La pila se asigna efectivamente en la SRAM de datos generales, y, en consecuencia, el tamaño de pila solo está limitado por el tamaño total de SRAM y el uso de la SRAM.

Todos los programas de usuario deben inicializar el SP en la rutina Restablecer (antes de que se ejecuten subrutinas o interrupciones). El puntero de pila (SP) es de lectura / escritura

accesible en el espacio de E / S. Se puede acceder fácilmente a la SRAM de datos a través de los cinco modos de direccionamiento diferentes admitidos en la arquitectura AVR.

El espacio de memoria de E / S contiene 64 direcciones para las funciones periféricas de la CPU como Registros de control, SPI y otras funciones de E / S. Se puede acceder directamente a la memoria de E / S o como las ubicaciones del espacio de datos después de las del archivo de registro, 0x20 - 0x5F. Además, este dispositivo tiene espacio de E / S ampliado de 0x60 - 0xFF en SRAM.

El espacio de la memoria del programa está dividido en dos secciones, la sección del programa de arranque y la sección del programa de la aplicación. Ambas secciones tienen bits de bloqueo dedicados para escritura y protección de lectura / escritura. La instrucción SPM que escribe en la sección de memoria Flash de la aplicación debe residir en la sección Programa de inicio.

Durante las interrupciones y las llamadas a la subrutina, el Contador de programa (PC) de la dirección de retorno se almacena en la Pila. La pila se asigna efectivamente en la SRAM de datos generales, y, en consecuencia, el tamaño de pila solo está limitado por el tamaño total de SRAM y el uso de la SRAM.

Todos los programas de usuario deben inicializar el SP en la rutina Restablecer (antes de que se ejecuten subrutinas o interrupciones). El puntero de pila (SP) es de lectura / escritura

accesible en el espacio de E / S. Se puede acceder fácilmente a la SRAM de datos a través de los cinco modos de direccionamiento diferentes admitidos en la arquitectura AVR.

El espacio de memoria de E / S contiene 64 direcciones para las funciones periféricas de la CPU como Registros de control, SPI y otras funciones de E / S. Se puede acceder directamente a la memoria de E / S o como las ubicaciones del espacio de datos después de las del archivo de registro, 0x20 - 0x5F. Además, este dispositivo tiene espacio de E / S ampliado de 0x60 - 0xFF en SRAM.

Interrupciones

Un módulo de interrupción flexible tiene sus registros de control en el espacio de E / S con un bit de habilitación de interrupción global adicional en el registro de estado. Todas las interrupciones tienen un vector de Interrupción separado en la Tabla de vectores de interrupción. Las interrupciones tienen prioridad de acuerdo con su posición de vectores de interrupción. Cuanto menor sea la dirección del vector de interrupción, mayor será la prioridad.

Fuente: 8-Bit AVR Core

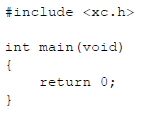

Comentarios

Publicar un comentario